|

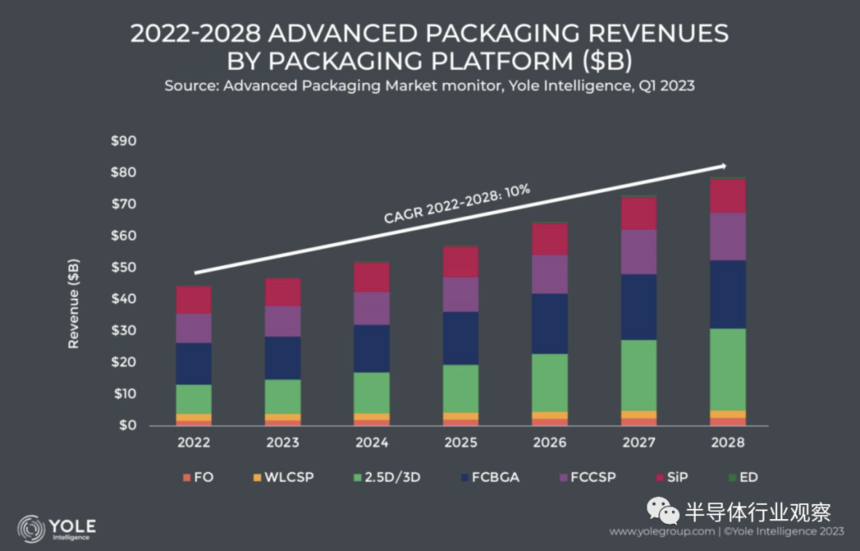

���M(j��n)���b���P(gu��n)עʲô�����߰� �M�ܲ��������ʹ����߀δ�ձ飬�����A(y��)�y(c��)�Q��һ����(sh��)�F(xi��n)�����ɞ�����ИI(y��)�µ��Α�Ҏ(gu��)�t��׃�ߡ� �~�ƿƼ��ژI(y��)��(n��i)�������TGV3.0���LJ�(gu��)��(n��i)����ͨ���g(sh��)�����I(l��ng)�ߣ������_�l(f��)���������S���ɻ��塢3D�Y(ji��)��(g��u)������Chiplet���S���ɵ����M(j��n)���b�I(l��ng)���Q������ ��������Դ�ڰ댧(d��o)�w�ИI(y��)�^�� �����߾��� �M�����w��(j��ng)��(j��)�����⣬�����M(j��n)���b�Ј�(ch��ng)�^�m(x��)���֏��ԡ�����(j��)Yole Group���µĈ�(b��o)�����c��һ����ȣ�2022 ����������L(zh��ng)�˼s 10%��2022��r(ji��)ֵ443�|��Ԫ���A(y��)Ӌ(j��)2022-2028���(f��)�������L(zh��ng)�ʣ�CAGR����10.6%����2028���_(d��)��786�|��Ԫ��

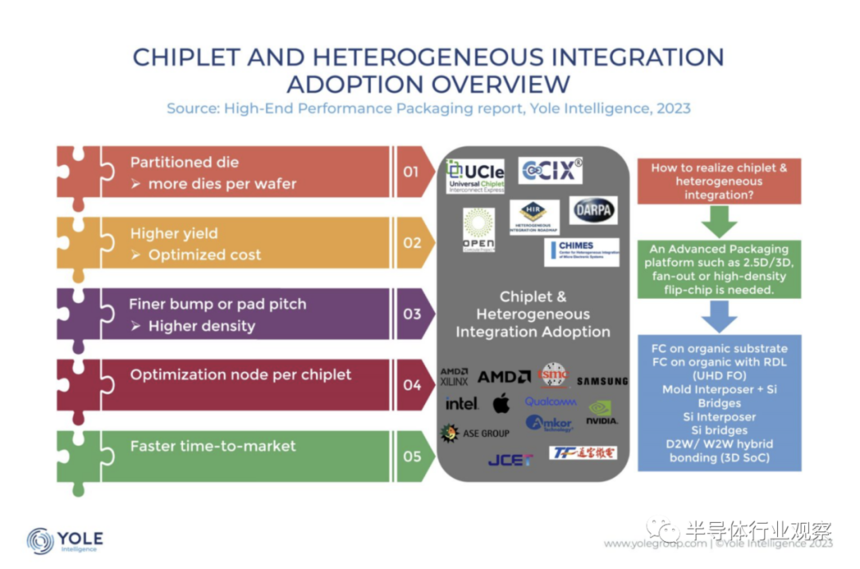

��(b��o)���M(j��n)һ��ָ�������ڌ�оƬ�c�����M(j��n)��(ji��)�c(di��n)���ɵĸ߶����ܷ��b�A(y��)Ӌ(j��)��2028�ꌢ���^160�|��Ԫ��ռ���M(j��n)���b�I(l��ng)���20%���ϡ��ڲ�ͬ�����M(j��n)���bƽ�_(t��i)�У�2.5D/3D ���L(zh��ng)��죬2022 ���� 2028 ��� CAGR �ӽ� 40%�����Ƿ������_�l(f��)���ļ��g(sh��)֮һ������ռ���^�� ����ǰ�e�k�� ECTC�����Ԫ���ͼ��g(sh��)��(hu��)�h���ϣ�Yole�ķ����������ˌ�(du��)���M(j��n)���bδ���l(f��)չ��һЩ������ Chiplet�ͮ���(g��u)���ɏص�׃�����M(j��n)���b ��Yole�������S��Ħ�����ɵķž��Լ�ǰ�ع�(ji��)�c(di��n)��(f��)�s�Ժͳɱ������ӣ����M(j��n)���b���ڳɞ錢����(g��)��Ƭ���ɵ���(g��)���b�е��P(gu��n)�I��Q���������п��ܽY(ji��)�ϳ�������M(j��n)�Ĺ�(ji��)�c(di��n)������(g��u)���ɺͻ���СоƬ�ķ������˹����ܡ��W(w��ng)�j(lu��)���Ԅ�(d��ng)�{�߶� PC �߶��Α�ȼ�(x��)���Ј�(ch��ng)��׃�ñز����١�ͨ�^���M(j��n)���b���g(sh��)��(sh��)�F(xi��n)�Į���(g��u)���ɿ��ھo����ƽ���Ќ�(sh��)�F(xi��n)���гɱ�Ч��Ķ�оƬ���ɣ��c���y(t��ng)���b���Ҳ�Ɍ�(sh��)�F(xi��n)��Խ�����ܡ�

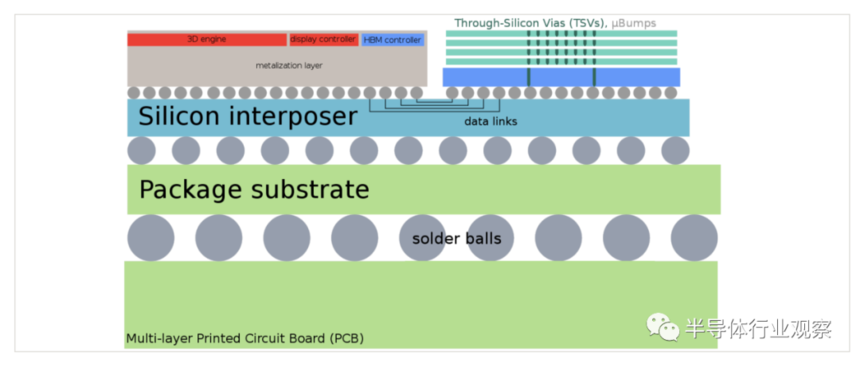

�ڷ��b��(n��i)���ɸ�����(sh��)������Դ�·��һ�Nͨ�^�ܼ����B����ͬ���ܷ��䵽���ɵ�ͬһ���b�еIJ�ͬоƬ�ķ��������Еr(sh��)�gҲ�s���ˣ���?y��n)�оƬ���ԁ��Բ�ͬ�������̲��M(j��n)�нM�b�� Octopart��һƪ�����Єt¶��Ҫ�������СоƬ�Įa(ch��n)Ʒ������Ҫ�O(sh��)Ӌ(j��)���ܡ���Ƭ����Ƭ֮�g���B���Լ����a(ch��n)���ԡ�chiplet���b���g(sh��)�����ܡ��r(ji��)��ͳ���Ȍ�(du��)chiplet�đ�(y��ng)��������(sh��)�|(zh��)�Ե�Ӱ푡�����(j��)�B�ӽ��|(zh��)�ͷ�ʽ�IJ�ͬ������chiplet���B�ķ��b���g(sh��)�ɷ֞����������b��Substrate packaging�������н�ӷ��b��Silicon-interposer packaging�����ٷֲ��� (RDL��Redistribution-layer ) ���b�Լ�Ƕ��ʽ��оƬ���B�� (EMIB��Embedded multi-die interconnect bridge )�� ���ȿ�������b�����еĻ����x�����ЙC(j��)���ϣ���?y��n)��@Щ���Ϻ����@�á��c���y(t��ng) PCB ��ƣ������B����ͨ�^�g�̹�ˇ��ɵģ�ԓ��ˇ��(d��)���ڰ댧(d��o)�w������ʹ�õ�������ˇ���@���������� 2D ����(g��u)���ɵ����绯���� ͨ�^���bоƬ�O(sh��)Ӌ(j��)��ѯB�������p�ɵ،�����(g��)��Ƭ���ܶȵ��B�ӵ������ϡ����⣬�c֮���P(gu��n)�IJ��Ϻ�����ɱ��O�ͣ���?y��n)�ԓ���g(sh��)����ه��оƬ���칤ˇ��ʹ���@�N���g(sh��)����Ҫȱ�c(di��n)�� I/O ���_�ܶȵͣ��Ķ��������@Щ���b�л��B�Ď����� ��ο����н�ӷ��b��ԓ���g(sh��)���w 2.5D �� 3D ���b���g(sh��)��оƬ���н���ϙM��(g��u)�� (2.5D) ��ֱ�ѯB (3D)�����ˌ�(sh��)�F(xi��n)��Ƭ֮�g�Ļ��B��ͨ�ţ������н�ӷ����ڻ������Ƭ֮�g���н�Ӿ���һ��(g��)��ӡˢ�·�壬���|(zh��)���Ǟ�СоƬ֮�g����B���ṩ���塣���B�Y(ji��)��(g��u)�ɽ����|�c(di��n)���Q���K�����ڷ��b��(n��i)���\(y��n)�еĹ�ͨ�� (TSV) ��(g��u)�ɡ��@Щ���ڌ���Ƭ�B�ӵ��н�ӣ������н���B�����B�ӵ����� BGA ���P�D���ķ��b���塣

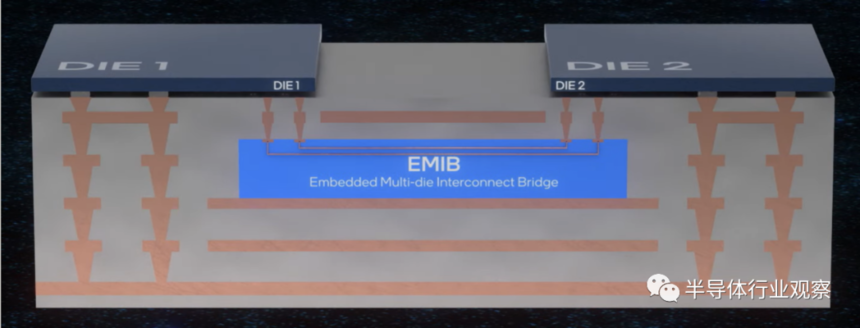

�@Щ�a(ch��n)Ʒ���и��ߵ� I/O �ܶȡ����͵Ĺ��ĺ��͵Ă�ݔ���t���@��ͨ�^�K�� TSV ֮�g��С���߾��L(zh��ng)�Ⱥ��g����(sh��)�F(xi��n)�ġ�ԓ���g(sh��)��Ψһ�@��ȱ�c(di��n)������ɱ����ӡ� �ٿ�RDL���b���g(sh��)���ٷֲ��� (RDL) ���b���g(sh��)��ʹ�û��壬���nj�늽��|(zh��)�ͽ���ֱ�ӳ��e�ھ��A������ϡ�ԓ���g(sh��)Ҳ�Q�顰�ȳ������g(sh��)�����˳��d��·�O(sh��)Ӌ(j��)����(g��u)����һ��(g��)���·ֲ��ӣ�ʹ��ÿ��(g��)СChiplet�ϵ� I/O �˿ڇ��@�O(sh��)����Ρ�ͨ�^�s���·���L(zh��ng)�ȣ�RDL �ṩ���ߵ���̖(h��o)�����ԣ����͵ēp�ĺ�ʧ�棩�� ����EMIB ���t��һ�Nʹ��Ƕ���ЙC(j��)�����еı��辧Ƭ��������оƬ��оƬ���B����ļ��g(sh��)����(j��)�a(ch��n)Ʒ�ɱ��^�ߵĆ��}����ͨ�^ʹ�þ��в�ͬChplet�Ę�ӷ��b����Q���@�N��Ϸ��b���g(sh��)�ǻ��ڻ���ͻ����н�ӵķ��b�ĽM�ϡ�ͨ��С�� 75 �ı���ӱ�Ϳ�ڻ����ϲ������γ�оƬ�g�B�ӣ��@Щ��Ƕ���ЙC(j��)������С� ԓ������ѭ HDI PCB ��ʹ�õ� ELIC �е���ͬ�뷨������ÿ�ӻ��B�Y(ji��)��(g��u)������(g��)оƬ�B�ӵ��^�����ЙC(j��)�������еă�(n��i)�ӡ����b�� EMIB ������һ��(g��)�����СоƬ֮�g�ṩ�ߎ����B�ӡ�

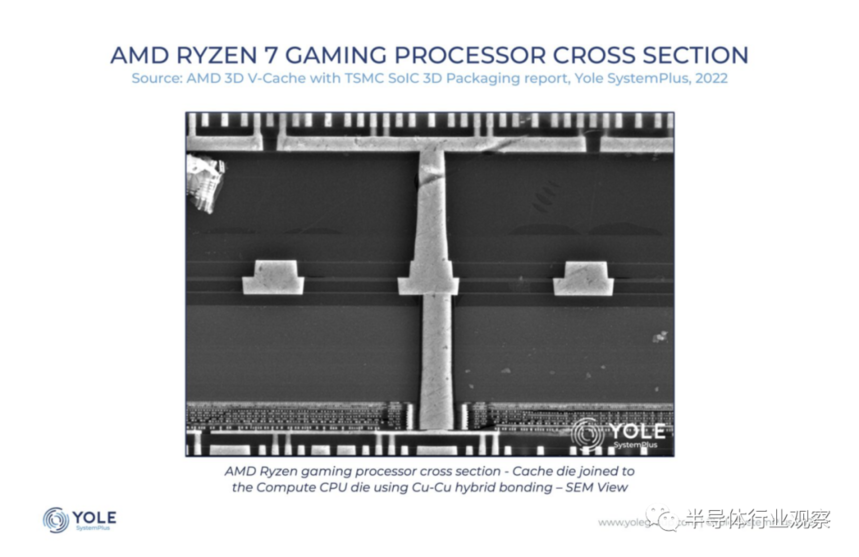

����I�ϟo̎���� Yole�������Џ�(qi��ng)�{(di��o)��ECTC �Ďׂ�(g��)��(hu��)�h���TӑՓ�˻���I�ϣ�hybrid bonding����������������ԓ���g(sh��)���ڳɞ鮐��(g��u)���ɺ�СоƬ���g��(n��i)�M�b���g(sh��)�M(j��n)�����P(gu��n)�I����?y��n)������S�ڷ��b��(n��i)���ܶȴ�ֱ�ѯB��ͬ��оƬ�� ����I�Ͽ����Ǿ��A�����A��wafer-to-wafer������Ƭ�����A��die-to-wafer������Ƭ����Ƭ��die-to-die��������Ҫ��(y��u)��(sh��)���ڣ������S 3D �����ѯB�Ԍ�(sh��)�F(xi��n)��ֱ�s�źͱ�����оƬ�ѯB���g(sh��)���ߵĻ��B�ܶȡ�������һ��(g��)���c(di��n)�Ǽ�(x��)�g���I�ό�(d��o)�¸��ߵĻ��B�ܶȡ��@Ҳ������ϵ�y(t��ng)��������Ч�ʡ��ٶ�Ҳ������ߣ���?y��n)���y(t��ng)���c(di��n)������������ʹ��ֱ�ӵ��~��(du��)�~�I�ϡ��@�γ��˷dz��o�ܵĻ��B���������ں��P��оƬ�Y(ji��)��(g��u)��һ���֣����������I�Ϗ�(qi��ng)�ȺͿɿ��ԡ�

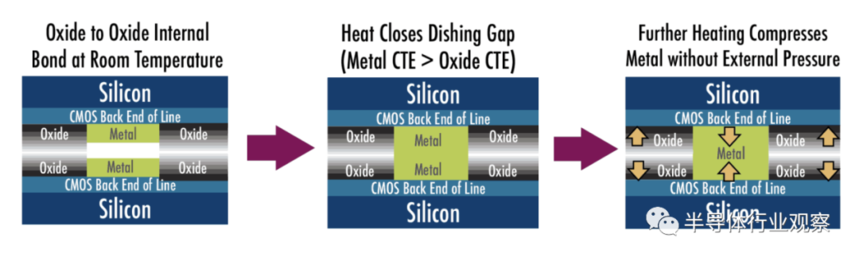

��BrewerScience����������I�����_��(chu��ng)���M(j��n)���b��(chu��ng)��δ�����P(gu��n)�I����?y��n)����I���ṩ��һ�N��Q���������Ԍ�(sh��)�F(xi��n)���ߵĎ����Լ����ߵĹ��ʺ���̖(h��o)�����ԡ����ژI(y��)�����ڌ���ͨ�^�U(ku��)չϵ�y(t��ng)��(j��)���B�������K�O(sh��)������ܣ���˻���I���ṩ������ǰ;�Ľ�Q�������܉�?q��)�����(g��)��Ƭ�cС�� 10 µm ��С���B�g�༯����һ�� ��Ҫ�˽����I�ϵĻ��A(ch��)֪�R(sh��)���t��Ҫ������(g��)�������}��ʲô�ǻ���I�ϡ���ʲôҪʹ�û���I���Լ��ķN�������m�����đ�(y��ng)�ã� BrewerScience��ʾ����(d��ng)��ӷ��b�ИI(y��)�l(f��)չ�����S���b�r(sh��)���Kͨ�^ʹ����Ƭ�ϵ�С�~�K���龧�A��(j��)���b��һ�N��ʽ���ṩоƬ֮�g�Ĵ�ֱ���B���K�ijߴ緶���� 40 µm �g�ൽ��K�sС�� 20 µm �� 10 µm �g�ࡣ���ǣ��@���dž��}���ڣ��sС���^ 10µm ׃�÷dz���������(zh��n)�ԣ����̎��������D(zhu��n)��һ�N�µĽ�Q�������^�m(x��)�sС�ߴ硣����I��ͨ�^��ȫ����ʹ���K�� 10 µm �������g���ṩ��Q����������ʹ��С���~��(du��)�~�B�Ӂ��B�ӷ��b�е���Ƭ�����ṩԽ�Ļ��B�ܶȣ�֧����� 3D �ķ��b��(j��)��(n��i)�������w�� ������I����һ�N�������I�ϣ���������I�� (SiOx) �cǶ����� (Cu) ��Y(ji��)�����γɻ��B����������(g��)�ИI(y��)���Q��ֱ���I�ϻ��B (DBI) ������I�ϔU(ku��)չ�����I�Ͻ�����Ƕ����ٺ��P���ں��I�ϣ����S���A���挦(du��)���B�ӡ���BrewerScience��(qi��ng)�{(di��o)��

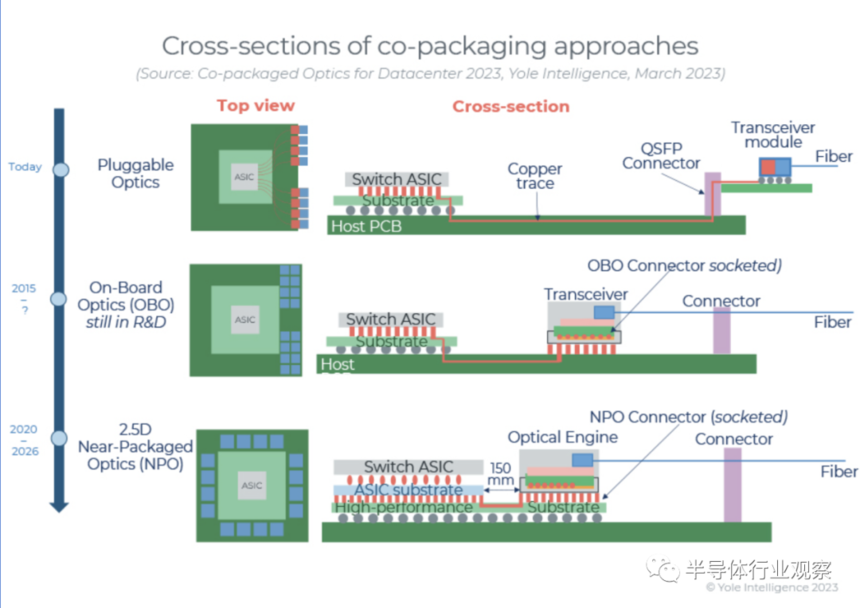

��?y��n)����I��ͨ�^�o���g�����~���P��ֱ�B����Ƭ�����A(D2W) �A�����A (W2W)���mȻ W2W ����I�����ڈD������I(l��ng)��Ͷ�����a(ch��n)���꣬���I(y��)���Դ����Ƅ�(d��ng) D2W ����I�ϵİl(f��)չ���@�N�l(f��)չ���M(j��n)һ����(sh��)�F(xi��n)����(g��u)���ɣ����ṩ��һ�N��(qi��ng)����`��ķ�ʽ��ֱ���B�Ӳ�ͬ���ܡ��ߴ���O(sh��)Ӌ(j��)Ҏ(gu��)�t��оƬ�� �c�����I�ϼ��g(sh��)��ȣ�����I�Ͼ����S����(y��u)��(sh��)�����������S��(j��) 3D �O(sh��)��ѯB����� I/O��(sh��)�F(xi��n)10 µm���µ��I���g�ࡢ���ߵă�(n��i)���ܶȡ��U(ku��)չ���������ӹ��ʡ�����ٶ�Ч�ʡ������������Ҫ���ڛ]�й��ʺ���̖(h��o)�pʧ����r��������ܡ� ���^ECTC�ϵ�һЩ�l(f��)���߄tՄ���˿��Ը��M(j��n)����I�ϼ��g(sh��)�İl(f��)չ����������I�Ϗ�(qi��ng)�ȡ���Ʒ��Ҳ���������g����Ⱦ���}Ҳ��(hu��)Ӱ푻���I�ϣ��mȻ��Ⱦ�L(f��ng)�U(xi��n)�������������g(sh��)�ߣ��������g��С���w����ֹ������Ӱ푸��� ���������ڳɞ���b�������x�� �����¼��g(sh��)��ECTC ߀ӑՓ���²��ϡ����У��������ڳɞ�����ڷ��b���P(gu��n)�I����֮һ���������S����(y��u)�c(di��n)������ߌ�(d��o)���ԡ��C(j��)е��(qi��ng)�ȡ��ͽ�늳���(sh��)�͵ͽ�늓p�ġ���߀�܉�(chu��ng)����(x��)���Ϳ��g�����SС�g�࣬���� CTE������Ûϵ��(sh��)����ͨ�����ڷ��b�������ЙC(j��)���ϸ��ӽ��衣 �@�N����Ҳ�ѽ�(j��ng)�� RF��HPC�����ӌW(xu��)�� CPO����ͬ���b��W(xu��)����(y��ng)����׃������������ ECTC �c��(hu��)�߿����ˇ��@��������Ͳ����н�ӵİl(f��)չ���������������W(xu��)Ժ�c��������(y��ng)�̺� IC ���幩��(y��ng)�����к������_�l(f��)�ɿ������ܵĽ�Q�����������_�l(f��)��һ��(g��)�I(l��ng)���Dz���о���壨 glass core substrates������ȡ�����y(t��ng) IC ������ЙC(j��)о��organic core�����@��Ҫ������ HPC �� RF ��(y��ng)�ó��� �����c����ȳɱ�����֮�⣬����߀���S����(y��u)�c(di��n)�������S��оƬ���ɵ����ͷ��b�У�ͬ�r(sh��)�ṩ���õ�ƽ���ȣ��@��(du��)�� HPC �� AI ��(y��ng)�ó������P(gu��n)��Ҫ����(d��ng)�l�ʳ��^ 5G �r(sh��)����ͽ�늳���(sh��)�����P(gu��n)��Ҫ���Õr(sh��) 6G �� 7G ���ٴ�����l�ʡ� ʹ�ò���о��(g��u)�� IC ������ò���������н�ӵ�����(zh��n)�c�����������Լ������܇��IJ������ЙC(j��)��֮�g�� CTE ����P(gu��n)���@���ܕ�(hu��)Ӱ푷��b�Ŀɿ��ԡ���һ��(g��)���}�ǣ���(g��u)���E���� build traces���Ľ��ٻ���ˇ�ȹ���y��Ȼ�����@��һ��(g��)����(du��)�^С�Ć��}�����Һܿ��ܕ�(hu��)�õ���Q�� �ձ����Ϲ��� Hoya �Լ�����(gu��)�� Corning �� Schott �ȹ�˾�����dȤ�M(j��n)��ԓ�I(l��ng)�� ��(j��)һƪ�}�顶Leveraging Glass Properties for Advanced Packaging����Փ�Ľ�B�����������M(j��n)���b�ṩ���S���C(j��)��(hu��)�������@�ă�(y��u)��(sh��)�Dz������ԡ�����^���w���������е�늓p�ģ��������ڸ��l�¡�����(du��)�^�ߵĄ��Ⱥ��{(di��o)������Ûϵ��(sh��)���������������о����Ͳ���ͨ�� (TGV) ���d�w��(y��ng)�õ�ճ�϶ѯB�е��N���ṩ�˃�(y��u)��(sh��)������߀���_�l(f��)���гɱ�Ч��Ľ�Q�����ṩ�˃�(y��u)��(sh��)����������ˇ�п����γ�����ʽ�Լ����� 100 �ĺ�ȣ��Ķ��ЙC(j��)��(hu��)��(y��u)����������(d��ng)ǰ�����췽���� ���������S�����ԣ�ʹ��ɞ���N���b��(y��ng)���������d�^�IJ��ϡ�����(du��)�ڹ裬������늚����ܽ�����늓p�ġ��@�ڸ��l��׃�ø�����Ҫ���@����һ���Ƅ�(d��ng)���g(sh��)���ܲ��õ�·������Ҫ�����x�����܉��ڱ���늳؉�����ͬ�r(sh��)���������֙C(j��)�Ĺ��ܡ� �{(di��o)�����ό��ԣ��� CTE���O��ش��M(j��n)��ʹ�ò��������N��ʽ�� 2.5D �� 3D ��(y��ng)�õ� TGV ���塣���⣬�Ա�����ĸ��|(zh��)���������γɲ���������ʹ�S���C(j��)��(hu��)�܉�?q��)��F(xi��n)�ɱ�Ч�档����չʾ����Ч�ӹ����������ṩ�ֶε�̎�����g(sh��)�� ���ó��͵�ͨ��ä���γ��ѽ�(j��ng)�õ��C�������ҿ������ìF(xi��n)�еĽ��ٻ����g(sh��)�ھ��A�������ʽ�IJ����Юa(ch��n)���dz��õ� Cu ������ܡ��������~���ͨ�Ŀɿ������ѵõ��C�����@Щ�l(f��)չʹ�����ɞ���һ�����b��(y��ng)�õ������d�^�IJ��ϡ� ���ǣ������ֹ��߀�]�д��������a(ch��n)�������ڷ��b�еļ�����δ������(n��i)��̫���ܣ���?y��n)�һЩ���m(x��)���ڵ�����(zh��n)����Ҫ��Q�����^����(j��)��(b��o)�����������幩��(y��ng)�� Absolics �����_ʼС�������a(ch��n)������Щ�r(sh��)��� 2024 ������a(ch��n)����о IC ���塣 ��ͬ���b��W(xu��) (CPO) �����ڳɞ�F(xi��n)��(sh��) ��(j��)Yole��(b��o)�����ڷ��b�I(l��ng)����P(gu��n)ע����һ��(g��)څ��(sh��) CPO �c�W(w��ng)�j(lu��)�͔�(sh��)��(j��)�����Ј�(ch��ng)���P(gu��n)�����@Щ�Ј�(ch��ng)�У���(du��)�������ӵ����������Ƅ�(d��ng)���ӻ��B�İl(f��)չ��������ٶȺͽ����ġ� CPO �Ƿ��b��Ӯa(ch��n)Ʒ����оƬ�������c����оƬ���B�� ASIC �� CMOS оƬ�����@һ�I(l��ng)��˾�M(j��n)���˺�����ECTC ���Ё��ԾW(w��ng)�j(lu��)�͔�(sh��)��(j��)���ġ�оƬ����(y��ng)�̡������S��OSAT���аl(f��)�C(j��)��(g��u)�Ͳ��Ϲ���(y��ng)�̵���ʾ���S���������P(gu��n)ע���M(j��n)�Ļ��壬���Ѓɂ�(g��)оƬ֮�g�Ļ��B��ͨ�^ IC ���匍(sh��)�F(xi��n)�ġ� Yole��ʾ�����^ȥ�� 50 ����Ƅ�(d��ng)���g(sh��)��(chu��ng)��ÿʮ���Ƴ�һ�Ρ��Ƅ�(d��ng)���������я��Z(y��)��ͨԒ�Ͷ��Űl(f��)չ�������� (UHD) ҕ�l���N����(qi��ng)�F(xi��n)��(sh��)/̓�M�F(xi��n)��(sh��) (AR/VR) ��(y��ng)�á��M�� COVID-19 ���l(f��)��(du��)��Ż��A(ch��)�O(sh��)ʩ����(y��ng)朮a(ch��n)�������h(yu��n)Ӱ푣���ȫ�����M(f��i)�ߺ���I(y��)�Ñ��^�m(x��)��(chu��ng)�쌦(du��)�W(w��ng)�j(lu��)���Ʒ���(w��)���������罻�W(w��ng)�j(lu��)���̄�(w��)��(hu��)�h��������ҕ�l��������̄�(w��)���Α�(y��ng)�ó���?q��)��^�m(x��)�Ƅ�(d��ng)���L(zh��ng)�� ÿ��(g��)��ͥ���˾��B�ӵ���(li��n)�W(w��ng)���O(sh��)���ƽ����(sh��)���������ӡ��S�����и��߹��ܺ����ܵ���(sh��)���O(sh��)��ij��F(xi��n)��Yole�^�쵽ÿ�궼�и��ߵIJ����ʡ����⣬����늱���ҕ�l�O(ji��n)�ء��t(y��)�������O(ji��n)�ء��B���(q��)��(d��ng)�����Ԅ�(d��ng)�������șC(j��)����(du��)�C(j��)����(y��ng)�õĔU(ku��)չ�@�����M(j��n)���O(sh��)����B�ӵ����L(zh��ng)�����Ƅ�(d��ng)�˔�(sh��)��(j��)���Ļ��A(ch��)�O(sh��)ʩ�ĔU(ku��)չ�� �����A(y��)�����p����ͬ���b��W(xu��) (CPO) ��^(q��)���R���y�r(sh��)�ڣ���?y��n)�ɲ��������pluggables���ѽ�(j��ng)���Ԍ�(sh��)�F(xi��n) CPO ���Z�ijɱ���(ji��)�s�͵��ġ�CPO ��ȫ�沿��ֻ��(hu��)�ڿɲ�ι����ñM�r(sh��)�ŕ�(hu��)�l(f��)���������ڽ����ăɴ��_�P(gu��n)ϵ�y(t��ng)�У����y�c�ɲ��ģ�K��(j��ng)��(zh��ng)�����ɲ��ģ�K�ں��L(zh��ng)һ�Εr(sh��)�g��(n��i)�Ԍ������x��CPO ��������ڔ�(sh��)��(j��)���� (DC) �еľW(w��ng)�j(lu��)��Ч���ܵ��V���P(gu��n)ע��Yole�ķ����������c DC �Ŀ�������ȣ��W(w��ng)�j(lu��)��(ji��)ʡ�Ĺ��Ŀ��Ժ��Բ�Ӌ(j��)��ֻ�� Broadcom��Intel��Marvell ������һЩ CPO ���c�ߕ�(hu��)�����н�Q���������Ј�(ch��ng)�����˝M���Ј�(ch��ng)������K�Ñ����� CPO �Ŀ����ԣ� �S�� 6.4T ��ģ�K�ĵ�����CPO �Ϳɲ�ι�W(xu��)����֮�g�ļ��Ҹ�(j��ng)��(zh��ng)���ܕ�(hu��)�� 2029 �굽�����Õr(sh��) CPO ϵ�y(t��ng)�еĶ���(g��)���g(sh��)�ϵK�����õ���Q��Ȼ�����հl(f��)���ИI(y��)���������ڄ�(chu��ng)�����Ƅ�(d��ng)�ɲ�ι�W(xu��)�Ј�(ch��ng)���� CPO ϵ�y(t��ng)��(sh��)�F(xi��n)�W(w��ng)�j(lu��)��(y��ng)�õ�������؛֮ǰ���ɲ�Ό�����(li��n)�Ϸ��b��ʽ����W(xu��)���挢�ڸ�����Ӌ(j��)���δ���ֽ�ϵ�y(t��ng)�Ы@�ø����ռ������@�C(j��)���W(xu��)��(x��) (ML) ϵ�y(t��ng)����(y��ng)�� Nvidia �� HPE �İ��� Ayar Labs��Intel��Ranovus��Lightmatter��AMD��GlobalFoundries ���ڃ�(n��i)�Ĺ��I(y��)���B(t��i)ϵ�y(t��ng)ȡ���˲��e(cu��)���M(j��n)չ��Ӌ(j��)���� 2024 ���� 2026 ��֮�g��(sh��)�F(xi��n)�a(ch��n)Ʒ��������؛. Yole�A(y��)Ӌ(j��)�� 800G �� 1.6T �ɲ��ģ�K��(hu��)���ܚgӭ����?y��n)��������?100G �� 200G �β��L(zh��ng)��W(xu��)��������˿����� QSFP-DD �� OSFP-XD ����Ҏ(gu��)�����Լ��g(sh��)�ͳɱ�Ч��ķ�ʽ��(sh��)ʩ���������늚��W(xu��)�ܶȡ����������ԴЧ�ʶ��ԣ��ɲ������Ҏ(gu��)��֧�� 6.4T �� 12.8 �������������ܵ����ơ����ڲ��÷���ʽ늚��O(sh��)�䣬���ĺ͟�������ɞ�δ���ɲ�ι�W(xu��)�������������ء�ʹ�ù���Ӽ��g(sh��)ƽ�_(t��i)�Ĺ�ͬ���bּ�ڿ˷���������(zh��n)�� Yole�M(j��n)һ��ָ�������ɲ��ģ�K�Ј�(ch��ng)����(y��ng)��ѽ�(j��ng)���ơ������������ɽM������(y��ng)�̡����a(ch��n)�l(f��)�����ͽ�������W(xu��)�ӽM����TOSA �� ROSA���Ĺ�W(xu��)��˾����·��(f��)��������(sh��)����̖(h��o)̎���� (DSP) �� PCB���Լ��M�b/�y(c��)ԇ�����̡����@�ӵĶ��(y��ng)���Ј�(ch��ng)ģ���У��漰�S�ͬ�Ĺ���(y��ng)�̡����⣬һ��(g��)�_�P(gu��n)���ж���(g��)��ͬ�ɲ��ģ�K�Ļ��������������ИI(y��)���`���ԡ��@Щ��Ŀǰ��(y��u)�� CPO ����Ҫ��(y��u)��(sh��)�����ߌ���(y��n)����ه����ӌW(xu��)���{��߶ȼ��ɵĹ�W(xu��)��оƬ�����dz���Ҫ�µĹ��������ʹ����S���@��(du��)�ڂ��y(t��ng)��������I(y��)���f�ǟo�����ܵġ� ��YoleҲֱ�ԣ��M�ܸ߶�CPO��Q����������������Ҫᘌ�(du��)�������\(y��n)�I(y��ng)�̣������д���Ҏ(gu��)ģ�^С����I(y��)��(sh��)��(j��)������δ�������µĻ��B���g(sh��)����˼��g(sh��)�����^�����c(di��n)���@��ζ������ʹ CPO �ɞ��������g(sh��)���ɲ��ģ�K�� CPO �ڼ��g(sh��)�ϻ�(j��ng)��(j��)�ϲ����еĎׂ�(g��)��(y��ng)�����Ԍ��кܸߵ����������L(zh��ng);��(y��ng)�ú�߅����(sh��)��(j��)���ġ����Yole�A(y��)Ӌ(j��)�ɲ�μ��g(sh��)��δ�� 10 ���(n��i)����(hu��)����̭��Ȼ�����ɲ�ι�W(xu��)�ИI(y��)���ܕ�(hu��)���ϣ��� CPO �Ј�(ch��ng)���γɶ��(y��ng)���̘I(y��)ģʽ�� δ����Ŭ��������(zh��n) ��(j��)Yole��B����ECTC�ϣ����߀Մ?w��)���һЩ��B�漰�ȳ��ͷ��b�������������˄t�о��˲������塣���⣬߀ӑՓ�˶�N���B���g(sh��)���K��TSV��RDL�������н�Ӷ��ڽ�(j��ng)�v���g(sh��)���M(j��n)�� Yole���꣬���^ȥ�����У��댧(d��o)�w����(y��ng)�?zh��n)ܵ��?Covid-19��оƬ�Ͳ��϶�ȱ����r������@�ڸ���(g��)����������Ɖģ����_ʼ��ʹ�ط�����Ͷ�Y�ڱ����댧(d��o)�w���a(ch��n)�� �� ECTC������ӑՓ�� CHIPS ���������M(j��n)���b���뱱����Ŭ�����^�쵽��������(y��ng)朲�ͬҪ��֮�g�ď�(qi��ng)��f(xi��)���ͻ���P(gu��n)ϵ�����а����O(sh��)Ӌ(j��)���O(sh��)�������̡����Ϻ��O(sh��)�乩��(y��ng)�̡��аl(f��)�C(j��)��(g��u)���� OSAT�� ����������(gu��)�_չ�����M(j��n)�İ��b�аl(f��)���(d��ng)�⣬Ŀ��(bi��o)֮һ��֧�֏��аl(f��)��������̘I(y��)�����w�ƣ�����˾һ���J(r��n)����Ҫ����ĝ����ҿ��g���@��Ҫ���A(ch��)�O(sh��)ʩͶ�Y���@Ҳ��Ҫ�r(sh��)�g��������(gu��)���߰��Ąڄ�(d��ng)���ɱ������ܶ�ȱ���Y��������Ȼ��K����(gu��)��(n��i)����(y��ng)朵İl(f��)չ���ښW�ޣ�ͬ�ӵ�����Ҳ�m�á� ��(j��)���b֧�ֵĮ���(g��u)���������ڮ�(d��ng)�����a(ch��n)��(j��)ǰ�˹�(ji��)�c(di��n)�ɱ����ߡ��y�ȸ����@һ��(sh��)���(q��)��(d��ng)�ġ��Ěvʷ�Ͽ������b��һ��(g��) OSAT �I(y��)��(w��)������?c��)��@��(g��)�I(l��ng)����Ȼ�dz���Ҫ�������_(t��i)�e늺� IDM���������Ǻ�Ӣ�ؠ��������^ȥʮ������������M(j��n)�ĺ�˽�Q������������������ǰ�������팍(sh��)�F(xi��n)2.5D �� 3D ��Q������������н�ӡ����ͻ���I�ϡ� �M�㔵(sh��)�ֻ���AI �d���Լ��W(w��ng)�j(lu��)��5G ���Ԅ�(d��ng)�{���܇�������L(zh��ng)�������ϵ�y(t��ng)Ҫ�������ˮƽ���܃Hͨ�^�p�ٹ蹝(ji��)�c(di��n)��M�㣬��?y��n)����P(gu��n)�ijɱ��ͮa(ch��n)���pʧ����ˣ�ע���������ڸ�(j��)���b�ϣ��Ԍ����Ը�(j��)����칝(ji��)�c(di��n)�Ĺ�о������һ���Խ���ϵ�y(t��ng)�ɱ��� ���M(j��n)���b���e�Ǹ߶����ܷ��b����ه�ڿ˷�������(g��)��Ƭ������ͬһ���b�С������Ƭ֮�g���g�ࡢ���B�ܶȺ͎������������(zh��n)����ˣ�ԓ�ИI(y��)���ڌ����|(zh��)���ɺͻ���I�ϣ�ͬ�r(sh��)Ҳ���о����гɱ�Ч����M(j��n)���ܵ��²����Լ� CPO ���¼��g(sh��)���Ԍ����M(j��n)���b������һ��(g��)�µ�ˮƽ���ԝM����һ������������ |